I2C Bus is IoT best friend

IoT designers should thank Philips Semiconductors company everyday for inventing the I2C bus in the 80s (I2C means Inter-Integrated Circuit). Two wires only and several ‘masters’ can communicate synchronously to several ‘slaves’. In comparison, SPI (with stands for Serial Peripheral Interface) needs four wires, plus one wire for each ‘slave’.

I2C is the most common wording but one calls it also I2C or IIC.

I2C bandwidth is not too bad: from 100 kHz (Standard) to 400 kHz (Fast) modes (special modes up to 5MHz). All modes are compatible with the 100 kbit/s standard mode, but combining devices of different capabilities on the same bus can cause issues.

With the I2C standard 7-bit address space, you can address up to 128 (126 with reserved adresses) devices. Hence, with a 10-bit address space, one can address up to 1024 (1008) slaves!

At Voltanode, we use extensively I2C bus in most of our designs. For your information SMBus (System Management Bus) is a subset of I2C. There is an extensive description of the I2C bus on Wikipedia there.

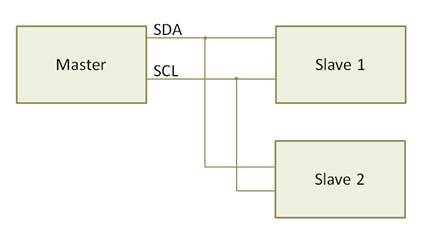

Bus Architecture and Protocol

The two wires (or lines) of the I2C bus are called SDA (Serial Data Line) and SCL (Serial Clock Line). It’s the current active master which generates the ‘master’ clock signal.

When a master wants to speak with a slave, it initially sends out a 9-bit packet over the data line specifying which device (slave) it wants to talk to. At the logical level, it pulls the SDA line low while the SCL remains high. In order to specify which slave it wants to speak to, it sends out a frame including the slave 7-bit address and a Read/Write (R/W) bit (and ACK bit as well).

If you have a lot of slave devices, you can opt for a 10-bits address space. The first ‘message’ is then decomposed into 2 messages of 9 bits.

If two masters want to communicate with a slave at the very same time, the rule is first come, first served.

The slave acknowledges (or not if it is busy) and then the data (a 8-bit workload inside a 9-bit packet with ACK) is sent from the master to the slave or vice versa. If the slave needs time to process the data, it can perform an operation called clock stretching, by holding the SCL line low after its ACK bit, which will prevent the master from sending data until the line is released.

Finally, the master terminates the session by triggering the SCL line from low to high followed by the SDA triggered from low to high. The bus is then opened up for other masters to communicate. If the master wants to send several messages and keeping the control of the bus, it can use a repeated start condition instead of the stop condition.

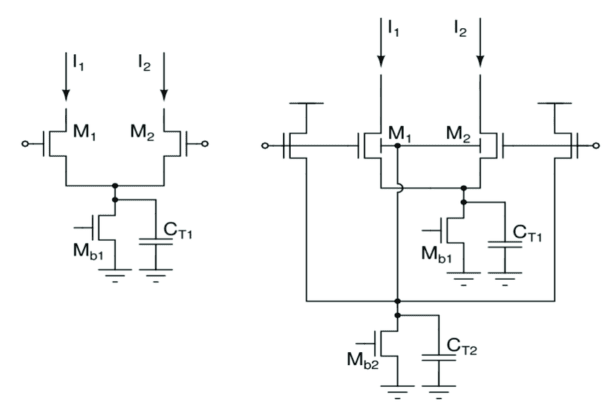

I2C Bus Capacitance

With so much adresses capability, there may be a bus capacitance issue, especially with PCB design constraints. I2C bus must compliant to a limit of 400 pF (Standard mode) or 500 pF (Fast mode) as maximum capacitance. In case your design reach this limit, you’ll have to divide the I2C bus into two separate buses, using a I2C Buffer. We prefer using buffer than multiplexers because buffers isolate capacitance from one bus to another.